Interconnect Metal Recess Using Functional Water Solutions

Date Published 2022 | Conference materials

To access our resources you will need to be a member of UltraFacility, log in to your account or purchase a membership to view this content.

For the dimensional scaling and performance enhancement of upcoming semiconductor devices, metal wire lines and space minimization are required. However, due to the technical limitation of mask locational alignment accuracy, wiring layer has short circuits and semiconductor performance deteriorates. To prevent short circuit by the misalignment, metal recess technology with etch back metal layer as atomic scale to fill dielectrics and create allowable gap length is required. Furthermore, wire metal has been changed to make interconnect line resistance lower from copper (Cu) to cobalt (Co) and molybdenum (Mo), new wet solutions which are optimize for each is demanded

Related content

Deconstructing the Challenges of Facility 2.0: Device Complexity Drives Facility Complexity

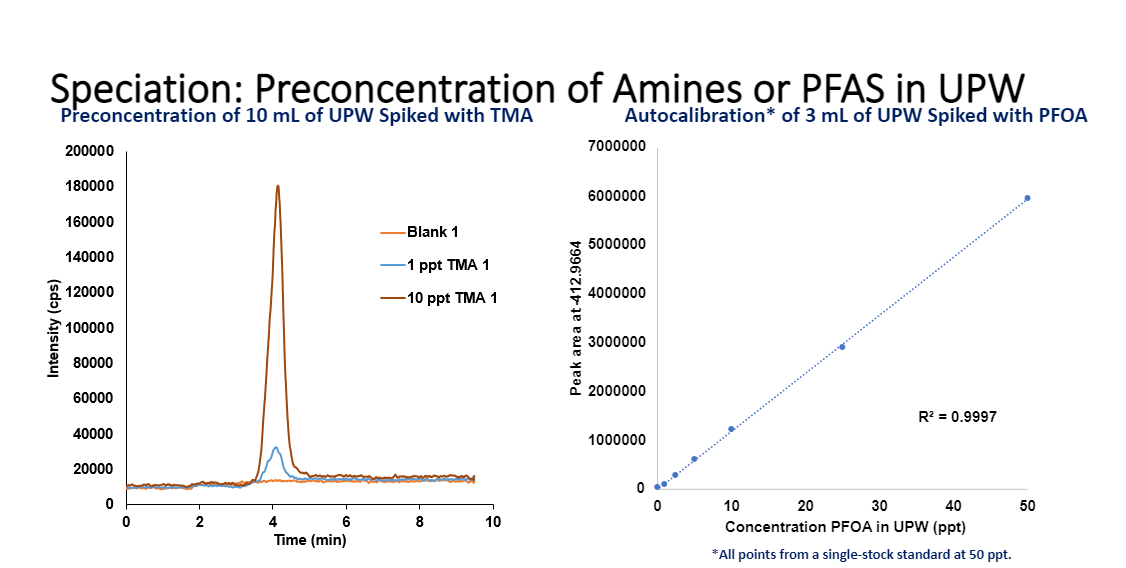

Online Automated Determination of Organic Contaminants in Semiconductor Grade Chemicals

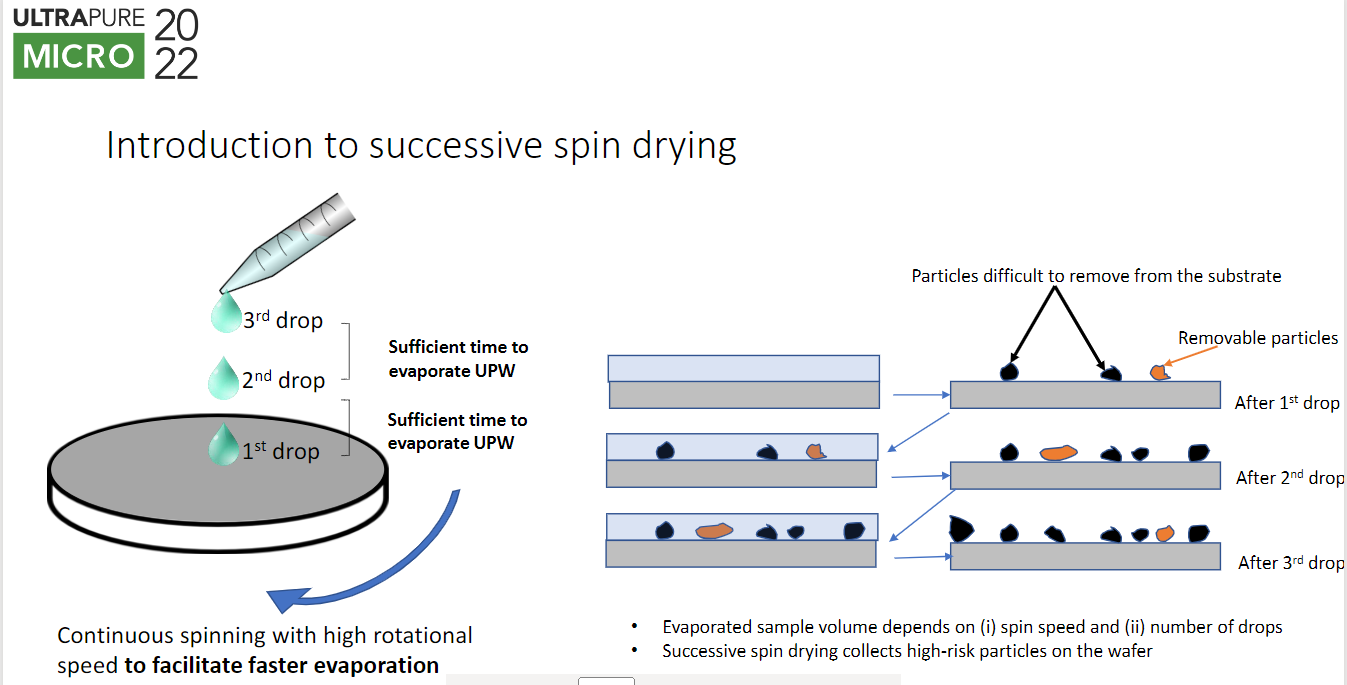

On-wafer defectivity analysis of UPW with successive spin drying

Evaluating the Risk of Metal Contamination from Wet Cleaning of Silicon Wafers by HF-Last Process

Back to results